HOPE²D | Start: 01.10.2024

Prof. Dr. Rolf Drechsler, Christina Sophie Viola Plump, Jan Zielasko

Im Projekt HOPE²D befassen sich die Studenten mit der Optimierung von Hardwarelayout für die Chipentwicklung. Bei der Implementierung logischer Funktionen auf Computerchips tragen unter anderem die Länge der Leitungen sowie mögliche Überkreuzungen der Kabel zu erhöhten Kosten bei. In diesem Zusammenhang beschäftigen sie sich darum mit der Minimierung von Kreuzungen, was ein NP schweres Problem darstellt. Deshalb ist das Ziel des Projekts die Entwicklung Algorithmen, welche die Kabelkreuzungen minimieren und trotzdem eine effiziente Laufzeit haben. Dafür werden funktionsevaluationsbasierte Techniken genutzt, wie Ant-Colony-Optimization oder Simulated Annealing, sowie Heuristiken, basierend auf dem Dijkstra Algorithmus. Diese haben die Studenten anhand ihrer Laufzeit, Qualität der Lösungen und deren Fähigkeit komplexere Probleminstanzen zu lösen bewertet und verglichen.

EIO4Future | Start: 01.10.2023

Prof. Dr. Rolf Drechsler, Christopher Metz, Christina Sophie Viola Plump

ElO4Future beschäftigt sich mit der Thematik der endlosen Optimierung. Damit bezeichnet man dynamische Optimierungssituationen, in denen sich Parameter oder Ziel der Optimierung während der Optimierung ändern können. Typische Anwendungsbeispiele hierfür sind zum Beispiel der Strommarkt oder auch die Routenplanung im Zugverkehr. Auch im Spielbereich finden sich viele Anwendungen. Im Projekt sollen Techniken zur dynamischen Optimierung entwickelt und im Prototypen eines Frameworks umgesetzt werden, damit ihre Performanz untersucht werden kann.

GenArC | Start: 01.10.2022

Rolf Drechsler, Martha Schnieber, Jan Kleinekathöfer

Logische Schaltungen sind in einer Vielzahl rechenintensiver Anwendungen wie Kryptographie, Signalverarbeitung, IoT-Geräten, anpassbaren Prozessoren sowie in kommenden KI-Architekturen involviert.

Viele dieser Anwendungen bringen jedoch hohe Anforderungen an die Hardware mit sich: So darf beispielsweise ein Chip, der sich auf einer kleinen ID-Karte befindet nicht zu groß sein, und ein Schaltkreis in einem mobilen Gerät sollte nicht zu viel Strom verbrauchen. Gleichzeitig möchte man jedoch, dass Eingaben auch schnell verarbeitet werden.

Mehr Infos

Webseite des ProjektesIot4U | Start: 01.10.2021

Prof. Dr. Rolf Drechsler, Dr. Vladimir Herdt, Sören Tempel, Sallar Ahmadi-Pour

Internet of Things (IoT) Geräte bieten intelligente Funktionen mit einem hohen Vernetzungsgrad. Für Zukunftsthemen wie Smart Homes und Smart Cities bilden sie eine elementare Grundlage. Für die Umsetzung ist ein hohes Maß an Sicherheit und Fehlerfreiheit von großer Bedeutung. In diesem Zusammenhang hat die moderne, offene und freie Befehlssatzarchitektur RISC-V enorm an Bedeutung gewonnen. RISC-V ist sehr modular aufgebaut und wurde von Grund auf so entwickelt, dass benutzerdefinierte Instruktionssatzerweiterungen integriert werden können, um Anwendungsfälle zu beschleunigen. Neben der Hardware (HW) spielt auch die Software (SW) eine sehr wichtige Rolle im Designprozess. Um eine parallele Entwicklung von HW und SW zu ermöglichen, werden virtuelle Prototypen eingesetzt, d.h. abstrakte Simulationsmodelle der HW, die die SW ausführen können. Gerade im IoT-Bereich sind auch Verifikationslösungen elementar, die Safety und Security Aspekte auf HW- und SW-Ebene abdecken.

Im Projekt IoT4U wollen wir die Studierenden an einem praktischen Beispiel an den modernen Systementwurf heranführen. Anhand von virtuellen und realen IoT-Geräten sollen Methoden und Techniken zur Verifikation der Funktionalität und Sicherheit erforscht werden.

Mehr InfosJARVIS4U | Start: 01.10.2020

Prof. Dr. Rolf Drechsler, Saman Fröhlich, Christopher Metz, Tim Meywerk

Maschinelles Lernen und Robotik geraten immer mehr in den Fokus der Öffentlichkeit. Sie bilden die Grundlage für einen technologischen Umbruch in der Gesellschaft und sind Ziel aktueller Forschung und Entwicklung.

Eine der prominentesten Anwendungen sind Home Assistants. Diese bündeln wichtige Anwendungsgebiete wie Digitale Bildverarbeitung, Spracherkennung und Web Suche in einem System. In dem Projekt JARVIS4U wollen wir durch die Entwicklung der Künstlichen Intelligenz (KI) JARVIS noch einen Schritt weitergehen und einen Life Assistant entwickeln. JARVIS soll dabei nicht nur das Leben im Zuhause erleichtern, sondern auch eine Erleichterung im Alltag sein, und zwar egal wo man ist. Konkret soll Dir JARVIS beispielsweise helfen bei: 3D-Navigation in komplexen Gebäuden (z.B. GW2), simulierte Anprobe neuer Kleidung oder Unterstützung beim Sport durch Erkennen und Korrektur von Fehlhaltungen etc. Im Projekt JARVIS4U wollen wir gemeinsam sinnvolle Anwendungen erarbeiten und diese implementieren. Zudem soll JARVIS auf kostengünstigen Endgeräten funktionieren, so dass die Teilnehmenden JARVIS auch im alltäglichen Leben benutzen können.

Mehr InfossystemXrunner | Start: 01.10.2019

Prof. Dr. Rolf Drechsler, Dr. Cornelia Große, Jil Tietjen, Jonas Wloka

Viele Systeme des modernen täglichen Lebens verwenden Software, die sie steuern. Oftmals beginnt das bereits morgens mit dem Drehen des Zündschlüssels im Auto auf dem Weg zur Arbeit oder bei dem Druck auf einen Knopf des Kaffeeautomaten zum Wachwerden. Eingebettete Systeme (mit oder ohne Betriebssystem) steuern den Alltag mit zunehmender Verbreitung. Selbst die Apollo-Missionen zum Mond benötigten (nach heutigen Maßstäben minimale) Computerunterstützung, um das Ziel zu erreichen.

Wer ein tiefes Verständnis für eingebettete Software, sowie den modernen Systementwurf in hardwarenahem Kontext erhalten möchte und/oder mehr über neuartige und effiziente Verfahren für automatische Analyse von Computerspielen bzw. Programmanalyse erfahren möchte, ist bei SystemXrunner der AG Rechnerachitektur richtig aufgehoben.

Mehr InfosDrive | Start: 01.10.2018

Rolf Drechsler, Daniel Große, Tim Meywerk, Saman Fröhlich

DRIVE steht für Design of Robust Intelligent Vehicles und ist ein Projekt der Arbeitsgruppe Rechnerarchitektur. Ziel ist es ein selbstfahrendes Modellauto zu bauen und dieses hin zu einem funktionierenden autonomen System zu entwickeln. Wichtige Aspekte dabei sind, dass das Auto robust gegenüber Störung und äußere Einflüsse ist und zuverlässig funktioniert. Zudem sollen Schnittstellen zur Verfügung stehen, die es ermöglichen über mobile Geräte auf das Auto zuzugreifen und Befehle auszuführen. Als Ausgangspunkt wird das Donkey Car verwendet, das bereits über einfache Sensorik und Aktuatorik verfügt und Deep Learning zur Steuerung einsetzt. Für die Entwicklung des Modellautos wurde an der Hardware gearbeitet, viele neue Sensoren wurden angebracht und das Design des Autos überarbeitet. Eine Hürde hierbei war es das Auto so zu gestalten, dass man mit dem limitierten Platz auskommt. Ein großer Fokus lag bei der Entwicklung auf dem Aspekt des Maschinellen Lernen, welches es dem Auto erst ermöglicht autonom zu fahren. Um nicht dauerhaft auf das Modellauto angewiesen zu sein wurde sich zudem stark mit der Entwicklung eines Simulators beschäftigt.

bugRunner | Start: 01.10.2017

Rolf Drechsler, Cornelia Große, Oliver Keszöcze, Kenneth Schmitz

Spiele und Software zur Unterhaltung gehören in der Informatik zur schönsten

Nebensache der Welt. %für den Zeitvertreib.

Die Ära der 8, 16 und 32-Bit Konsolen zeichnet sich in dieser Disziplin durch

besonders kultige Titel und Charaktere, wie zum Beispiel Super Mario, Yoshi,

Megaman, Donkey Kong und viele weitere aus.

Das Konzept der "Speedruns" stellt im Internet eine populäre Herausforderung

dar, derartige Spiele in möglichst kurzer Zeit (oder mit anderen Zielsetzungen)

entweder manuell oder "Tool-Assisted" (TAS) zu absolvieren.

Seit die Konzepte künstlicher Intelligenz, sowie maschinelles Lernen wieder

in großem Maße an Beliebtheit gewinnen, existiert die Idee, Computerspiele

automatisiert zu absolvieren oder Easter-Eggs, Fehler (Glitches) in der Software

zu entdecken. Ist das Ziel, ein Spiel in kürzester Zeit zu absolvieren, so ist von einem Speedrun die Rede.

In diesem Kontext werden sich die Studenten des BugRunner Projektes mit der

detaillierten Analyse von Spielesoftware (primär, jedoch nicht aus\-schließlich

der 8-32-Bit Konsolengeneration) auseinandersetzen.

Die Herausforderungen liegen dabei

1. in der Lokalisierung von Features, Bugs und weiteren Eigenschaften der Spiele sowie

2. der Programmierung eines Systems, das auf Basis dieser Informationen sowie mit Lernalgorithmen die Spiele löst.

Zu diesem Zweck sollen beispielsweise die Konzepte statischer und dynamischer

Programmanalyse, Codeinstrumentierung, Debugging, Profiling und moderne

Techniken aus dem Bereich der künstlichen Intelligenz und Deep-Learning

verwendet und verknüpft werden.

Das Verständnis und die Analyse solch systemnaher Software erfordert ein

grundlegendes Verständnis der zugrunde liegenden Hardware-Architektur.

Eine tief gehende Analyse (bis hin zur Verifikation) der ausgeführten Software

(und den Zwischenprodukten) ist ein integraler Bestandteil zum Entwurf

fehlerfreier Systeme.

Das Projekt orientiert sich somit sowohl am Profil für Sicherheit und Qualität

(SQ) von Soft- und Hardwaresystemen als auch an Künstliche Intelligenz,

Kognition und Robotik (KIKR) durch die verwendeten Lösungsalgorithmen.

AriCo Approximate Computing | Start: 01.10.2016

Rolf Drechsler, Daniel Große

Im Projekt Approximate Computing (AriCo) sollen drei Kernfragen beantwortet werden:

1. Was und wie kann ich approximieren?

2. Wie gut ist mein Ergebnis?

3. Wie profitiere ich davon?

Dafür soll Approximation durchgängig vom Algorithmus (Anwendungssicht) bis zur Hardware betrachtet werden. Das Hauptziel von AriCo ist es eine Plattform zu entwickeln, die es dem Anwender ermöglicht über die Ebenen hinweg an den „richtigen Stellen“ approximieren zu können (damit kann man sich den JPEG Header erhalten und das Bild geht nicht kaputt). Dies erlaubt es für die neusten Anwendungen (siehe z.B. Bereiche wie Suchmaschinen, Spracherkennung, Objekterkennung in Bildern) zu beschleunigen, zu kombinieren und weiterzuentwickeln.

Wer an Beschleunigung und Effizienzsteigerung auf Software- und/oder Hardwareebene oder dem Einsatz von Approximate Computing für die Anwendungen von morgen arbeiten möchte ist in AriCo richtig aufgehoben. Grundsätzlich bewegt sich das Projekt in ähnlichen Bereichen wie Praktische Informatik 1/2 und Technische Informatik 1. Wer Spaß an Algorithmen und Lösungstechniken hat, wird sich auch in AriCo wiederfinden.

Das Projekt ist für Studierende aus dem Bachelorstudiengang Informatik offen. Eine Weiterführung des Projektes im Masterstudiengang ist geplant. Das Bachelorprojekt bereitet auf die Masterprofile SQ und KIKR und teilweise auch DMI vor.

Generic Problem Solver (GPS) | Start: 01.10.2015

Rolf Drechsler, Oliver Keszöcze, Jannis Stoppe, Kenneth Schmitz

Das Lösen von Problemen gehört zu den Kernaufgaben der Informatik. Auch wenn dabei unterschiedlichste Anwendungsfelder betrachtet werden, lassen sie sich oft in Kategorien wie Sortierprobleme, Suchprobleme, Optimierungsprobleme, Entscheidungsprobleme, etc. einordnen. Ebenso sind die verwendeten Lösungsansätze oft ähnlich. Jede/r Informatiker/-in hat sicher schon mal ein Problem durch einen simplen Aufzählungs- oder Backtracking-Algorithmus gelöst.

Im Rahmen des Projektes wollen wir die Grundlagen für eine ähnliche Vorgehensweise zur Lösung von typischen Informatik-Problemen entwickeln. Ziel ist ein Framework, welches Informatiker/-innen ermöglicht, nicht nur einfache Such- oder Sortierprobleme-Probleme sondern auch komplexe Fragestellungen grob zu konfigurieren, um sie anschließend mit einem solve()-Aufruf zu lösen. Dafür sollen etablierte „Kern-Probleme“ der Informatik untersucht und in dem geplanten Framework entsprechend zur Verfügung gestellt werden. Die Ausgestaltung der Frameworks soll dabei im Laufe des Projektes definiert werden und kann z.B. eine Bibliothek, eine eigene Sprache (inkl. Übersetzer) oder ein komplett anderes Interface beinhalten.

Deep Game | Start: 01.10.2014

Rolf Drechsler, Daniel Große, Hoang Le

(erstes Projektsemester: Melanie Diepenbeck, Rolf Drechsler, Mathias Soeken, Hoang Le)

Das Projekt Deep-Game hat es sich zur Aufgabe gemacht, intelligente Computerspieler, sogenannte Agenten, für unterschiedliche Gesellschaftsspiele zu entwickeln. Es werden verschiedene algorithmische Ansätze verwendet, um möglichst gute Lösungen zu erzielen. Ein gemeinsames Merkmal der betrachteten Spiele ist es, dass jeder Zug eine Vielzahl möglicher Folgezüge hat. Dadurch entstehen sehr große Suchräume, die effizient traversiert werden müssen.

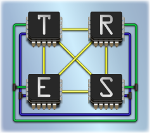

TRES | Start: 01.10.2014

Görschwin Fey, Fabian Greif, Heinz Riener, Carl Johann Treudler

Im Projekt sollen unterschiedliche Konzepte entworfen und prototypisch realisiert werden, die Thread Level Redundancy in Embedded Systems (TRES) effizient unterstützen.

In sicherheitskritischen Anwendungen wird für eingebettete Systeme eine extrem hohe Zuverlässigkeit gefordert, d.h. die Korrektheit der Funktion des Systems muss mit hoher Wahrscheinlichkeit gewährt sein. Insbesondere muss das eingebettete System auch dann funktionieren, wenn Teile des Systems, wie zum Beispiel einzelne Prozessoren, eine Fehlfunktion haben. Wenn das eingebettete System auch mit hoher Wahrscheinlichkeit einsatzbereit sein muss, also gleichzeitig eine hohe Verfügbarkeit des Systems notwendig ist, müssen meist Teile des Systems redundant auslegt werden. Diese Teile werden mehrfach realisiert.

Wenn die Hardware-Architektur entsprechend ausgelegt wurde, wird das durchgängig fehlerfreie Verhalten des eingebetteten Systems zu einer Software-Aufgabe. Die entsprechende Realisierung der Software ist jedoch nicht trivial. Zum Beispiel muss der Systemzustand typischerweise konsistent zwischen den redundanten Teilsystemen gehalten werden, so dass ein beliebiger Teil des Systems ausfallen kann, ohne Datenverlust zu verursachen. Gleichzeitig muss das gewünschte Zeitverhalten garantiert werden, wenn zeitkritische Steuerungsaufgaben ausgeführt werden.

CompTech | Start: 01.10.2013

Rolf Drechsler, Robert Wille, Oliver Keszöcze

Computing Technologies: The Next Generation

Im Rahmen des Projektes CT:TNG (Comp Tech: The Next Generation) wollen wir diese „nächste Generation“ von Computertechnologien kennenlernen und verstehen. Insbesondere soll dabei betrachtet werden, wie sich diese neuen Rechnersysteme entwerfen und nutzen lassen. Für Computersysteme, die vielleicht schon sehr bald unseren Alltag erreichen, wollen wir bereits heute ein Verständnis entwickeln und erste Anwendungen dafür umsetzen. Gleichzeitig wird dabei ein Verständnis vermittelt, wie konventionelle Computer entworfen werden und auf welche Grenzen wir dabei stoßen.

Mehr Informationen >>FaTNet | Start: 01.10.2012

Görschwin Fey, Carl Johann Treudler

Im Projekt FaTNet (Fault Tolerant Network) soll die Vernetzung von mehreren fehleranfälligen Knoten zur Erhöhung der Zuverlässigkeit des Rechensystems untersucht und demonstriert werden. Zu Beginn des Projektes wird eine kurze Einarbeitungsphase stattfinden. Hier eignen sich die Projektteilnehmer die Grundlagen an und untersuchen existierende Ansätze von fehlertoleranten Systemen, mit besonderem Augenmerk auf vernetzte Ansätze. Darauf auf-bauend sollen ein oder mehrere Lösungsansätze anhand eines von den Teilnehmern entwickelten Demonstrators dargestellt werden, z.B. durch einen mobilen Roboter. Der Demonstrator soll dabei aus mehreren eingebetteten Systemen und möglicherweise auch programmierbarer Logik bestehen. Durch die Möglichkeit der Fehler-Injektion im Demonstrator wird die Fehlertoleranz anschaulich dargestellt. Für die Implementierung soll der Grad der Fehlertoleranz bestimmt und verifiziert werden.

Mehr Informationen >>iTac | Start: 01.10.2012

Melanie Diepenbeck, Rolf Drechsler, Marc Michael, Mathias Soeken

In allen Bereichen hat die Informationsflut lawinenartig zugenommen. E-Mails, Webseiten, Dokumente, Soziale Netzwerke, Blogs, Zeitungen und diese Liste lässt sich beliebig fortsetzen. Die zentrale Gemeinsamkeit all dieser Informationsquellen ist Text. Täglich muss man dabei die relevante Information finden bzw. extrahieren. Um der Lage Herr zu werden, wird als Lösungsstrategie der Text überflogen, gefiltert oder einfach ignoriert. Dabei liegt der Text ja eigentlich bereits "verarbeitbar" im Rechner vor. Betrachtet man hier beispielsweise aktuelle Textverarbeitungssoftware, so beherrscht diese Rechtschreib- und Grammatikprüfung ziemlich gut. Im Kontext von Programmiersprachen entspräche dies aber etwa dem Niveau von Type-Checking, also der Überprüfung auf mögliche Typverletzung.

Im Projekt "iTac"(interpret Text and conclude) wollen wir Text automatisch durch Software verstehen und es ermöglichen Schlussfolgerungen zu ziehen. Damit schaffen wir die Basis für vielfältige Anwendungen: von der Zusammenfassung von Texten, dem Vergleich zweier Texte, die Steuerung per Texteingabe bis hin zum Entwurf eines Systems mit Hilfe natürlicher Sprache.

Chip4U | Start: 01.10.2011

Rolf Drechsler, Robert Wille, Mathias Soeken

Computerchips werden längst nicht mehr nur in komplexen Rechenanlagen oder dem heimischen PC verwendet. Nahezu jeder Bereich des alltäglichen Lebens wird mittlerweile durch sie erfasst. Ob in der Kaffeemaschine, im Auto, im MP3-Player oder dem Mobiltelefon – überall verrichten kleine und größere Schaltungen ihren Dienst. Doch während Computerchips heute wie selbstverständlich verwendet werden, stellt der Entwurf und Bau entsprechender elektronischer Systeme noch eine große Herausforderung dar. Dies soll im Rahmen des Projektes „Chip4U“ („Chip for you“) näher ergründet werden.

Konkret wollen wir die bisherige „Anwendersicht“ ablegen und selbst ein eigenes Computersystem mit der dazugehörigen Softwareanbindung entwerfen und realisieren. Dadurch wollen wir hinter die Kulissen blicken und näher betrachten, wie heutzutage eingebettete Systeme entstehen. Gleichzeitig sollen dabei die Grenzen heutiger Entwurfsmechanismen kennengelernt und Alternativen dazu überlegt werden.

McChip | Start: 01.10.2010

Rolf Drechsler, Görschwin Fey, Daniel Große und Heinz Riener

Im Projekt McChip (Multicore Chip) sollen der Entwurf und die Programmierung von Multicores betrachtet werden. Zu Beginn des Projektes wird eine kurze Einarbeitungsphase stattfinden. Hier eignen sich die Projektteilnehmer die Grundlagen und existierende Ansätze der Hardware- und Softwareentwicklung insbesondere im Hinblick auf Parallelität an. Darauf aufbauend sollen verschiedene Fragestellungen betrachtet und neue Ansätze entwickelt werden. Hierunter fallen Themen zum Entwurf von Multicore Chips wie neuartige Hardware-Architekturen sowie Programmiermodelle und -sprachen. Ebenso sollen Zuverlässigkeitsbetrachtungen durchgeführt sowie Anwendungen untersucht werden, die die neuen Möglichkeiten nutzen.

QBit | Start: 01.10.2009

Rolf Drechsler, Robert Wille, Mathias Soeken

In [QBit] sollen Algorithmen zum Entwurf von Quantencomputern entwickelt werden, die als vielversprechende Alternative zu traditionellen Rechenanlagen gelten. Im Fokus steht dabei die Entwicklung von Verfahren zur Synthese, Verifikation und Test entsprechender Schaltungen. Dabei müssen natürlich die Besonderheiten der neuen Technologie berücksichtigt werden. Am Ende soll ein zusammenhängender Entwurfsablauf entstehen, mit Hilfe dessen man Quantenschaltkreise für die Zukunft entwickeln kann.

PressemitteilungYMo | Start: 01.10.2008

Rolf Drechsler, Görschwin Fey, Christian Genz, Daniel Große

YMo beschäftigt sich mit der Korrektheit und Sicherheit von Anwendungen für Handys. Dabei soll das Open Source Betriebssystem Android eingesetzt und erweitert werden.

SPEED | Start: 01.10.2006

Rolf Drechsler, Görschwin Fey und Beate Muranko

Das Projekt SPEED beschäftigt sich mit der SPEzifikation und der darin Eingebetteten Dokumentation von Systemen. Es soll der Entwicklungsablauf von Eingebetteten Systemen mit dem Fokus auf Spezifikation und Dokumentation untersucht werden. Insbesondere soll dabei die Erarbeitung und Implementierung neuer Techniken im Vordergrund stehen.

Ein mögliches Ziel ist es einen Entwurfsablauf zu entwickeln, der automatisch aus einer natürlich-sprachlichen Eingabe das System, sowie die zugehörige Dokumentation erzeugen kann.

EXplayN | Start: 01.10.2005

Daniel Große und Andre Sülflow

(erste Projektphase: Nicole Drechsler und Rüdiger Ebendt)

Im Projekt EXplayN geht es um das Spielen (PLAY) von Strategiespielen. Sowohl 1-Personen-Spiele (Jigsaw-Schiebe-Puzzles, Rubiks-Cube, Solitaire, ...) als auch Mehr-Personen-Spiele (4-gewinnt, Mühle, Reversi, Dame, Schach,...) sollen analytisch (explain) untersucht werden, um Aussagen über die Schwierigkeit der Spiele treffen und Lösungsstrategien bewerten zu können. Dabei sollen vor allem Methoden (Algorithmen und Datenstrukturen), die aus dem Bereich des Schaltkreisentwurfs bekannt sind und dort erfolgreich eingesetzt werden, in diesem Kontext untersucht werden.

SATRIX | Start: 01.10.2004

Rolf Drechsler, Görschwin Fey und Daniel Große

Das Projekt SATRIX beschäftigt sich mit dem Erfüllbarkeitsproblem – oder kurz SAT von engl. satisfiability. Es soll der gesamte Ablauf von der Modellierung einer Fragestellung als SAT-Problem bis hin zur effizienten Lösung einer gegebenen Instanz betrachtet werden. Insbesondere sollen Fragestellungen aus dem Schaltkreisentwurf untersucht werden.

GAMELEON | Start: 01.10.2003

Nicole Drechsler

GAMELEON beschäftigt sich mit dem Entwurf Generischer Algorithmen und Methoden zur Anwendung Evolutionärer Algorithmen auf Optimierungsprobleme.

Als Schwerpunkt werden Anwendungsbeispiele aus dem Bereich der Graphentheorie und des computergestützten Schaltkreisentwurfs betrachtet.

FunTaskIC | Start: 01.10.2002

Rolf Drechsler und Görschwin Fey

Das Projekt FunTaskIC beschäftigt sich mit dem Entwurf von integrierten Schaltungen (IC=integrated circuit). Im Rahmen des Projektes soll eine durchgängige Entwurfsumgebung entwickelt werden, die den Entwickler ausgehend von der Spezifikation bis hin zur Schaltungsfertigung in automatischer Weise unterstützt. Die einzelnen Schritte sind nochmals im folgenden Bild verdeutlicht: Ausgehend von einer Idee wird eine textuelle Beschreibung erzeugt, die die Funktionalität im Wesentlichen festlegt. Nach einer Formalisierung dieser Beschreibung erhält man eine ausführbare Spezifikation, die anschließend (meist noch per Hand) in eine Hardware-Beschreibungssprache übersetzt wird. In der Folge wird die Beschreibung durch automatische Werkzeuge transformiert bis der fertige Chip entsteht. Besondere Bedeutung bei der Erstellung der Entwurfsumgebung soll Aspekten der Sicherheit und der Korrektheit zukommen, so dass die Verifikation schon in der frühen Entwurfsphase mit berücksichtigt wird. Die unterschiedlichen Aufgaben (tasks) sollen analysiert und optimiert werden. Anschließend sollen in der Gruppe Lösungsansätze diskutiert und umgesetzt werden. Und der Spaß (fun) darf natürlich nie fehlen ...

Die Arbeitsgruppe betreut seit ihrem Bestehen durchgehend studentische Projekte in der Informatik.

Die Arbeitsgruppe betreut seit ihrem Bestehen durchgehend studentische Projekte in der Informatik.