Currently we provide four RISC-V projects as open source at GitHub:

RISC-V VP

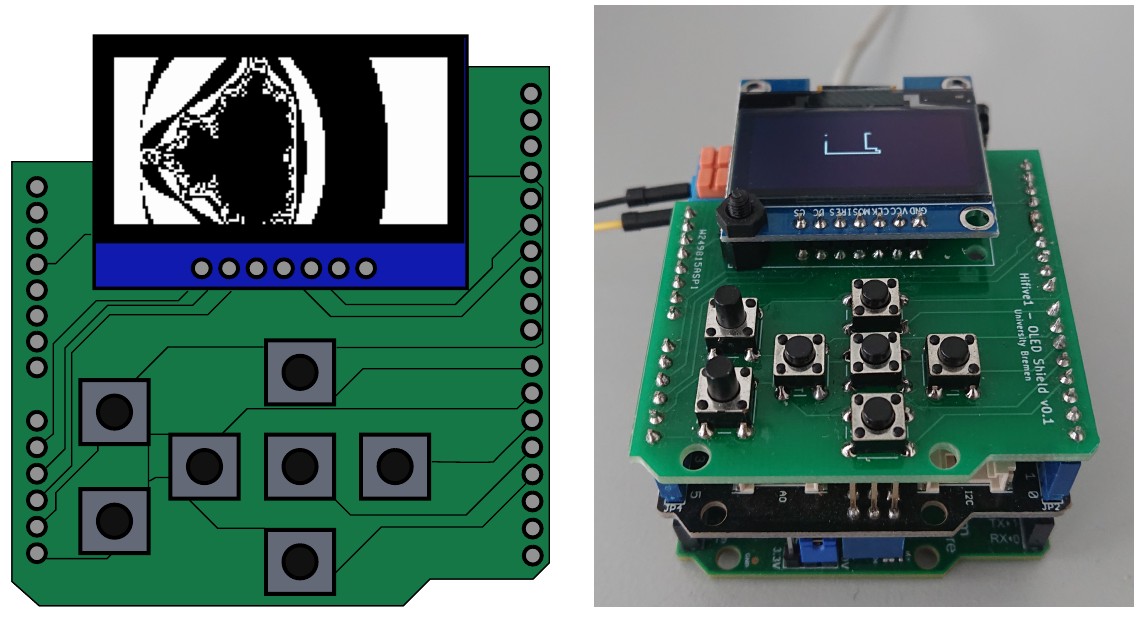

Website RISC-V VP: A configurable and extensible platform to build

virtual prototypes for RISC-V using C++/SystemC and TLM. Features include support for all standard RISC-V extension

for the 32 and 64 bit architecture including the M/S/U privileged architecture, advanced software debugging

capabilities using a GDB interface with an optional Eclipse GUI, a HiFive1 configuration and support for

graphical environment models, and support for several operating systems including RIOT, Zephyr, FreeRTOS

and Linux.

RISC-V VP: A configurable and extensible platform to build

virtual prototypes for RISC-V using C++/SystemC and TLM. Features include support for all standard RISC-V extension

for the 32 and 64 bit architecture including the M/S/U privileged architecture, advanced software debugging

capabilities using a GDB interface with an optional Eclipse GUI, a HiFive1 configuration and support for

graphical environment models, and support for several operating systems including RIOT, Zephyr, FreeRTOS

and Linux.MicroRV32

Website MicroRV32: A RISC-V register-transfer level platform written in

SpinalHDL and tailored for education and research. It integrates several peripherals alongside a 32 bit RISC-V core

interconnected with a generic bus system. Simulation and synthesis is supported through an accessible open source

tool flow that is Linux compatible. MicroRV32 supports bare-metal software and also small operating systems such as

FreeRTOS. A RISC-V VP configuration matching MicroRV32 is also available.

MicroRV32: A RISC-V register-transfer level platform written in

SpinalHDL and tailored for education and research. It integrates several peripherals alongside a 32 bit RISC-V core

interconnected with a generic bus system. Simulation and synthesis is supported through an accessible open source

tool flow that is Linux compatible. MicroRV32 supports bare-metal software and also small operating systems such as

FreeRTOS. A RISC-V VP configuration matching MicroRV32 is also available.SymEx-VP

Website SymEx-VP: Enables concolic testing for verification of RISC-V software

at the assembly level. Technically SymEx-VP is build upon RISC-V VP and integrates a concolic testing engine that supports

the 32 bit RISC-V instruction set architecture.

SymEx-VP: Enables concolic testing for verification of RISC-V software

at the assembly level. Technically SymEx-VP is build upon RISC-V VP and integrates a concolic testing engine that supports

the 32 bit RISC-V instruction set architecture.SymSysC

WebsiteSymSysC: An effective approach for verification of real-world SystemC TLM peripherals using modern C++ symbolic execution tools. It is a lightweight SystemC peripheral kernel that enables an efficient integration with the modern symbolic execution engine KLEE and acts as a drop-in replacement for the normal SystemC kernel on pre-processed TLM peripherals.

Prof. Dr. Rolf Drechsler

Prof. Dr. Rolf Drechsler