Ich beschäftige mich mit der formalen Verifikation von Schaltkreisen auf Gatterebene, insbesondere von approximierten Schaltkreisen. Hierbei zeige ich, dass die formale Verifikation von bestimmten approximierten Schaltkreisen in polynomieller Zeit und polynomiellem Platz durchführbar ist, indem ich polynomielle obere Schranken für die Komplexität der Verifikation bestimme.

Polynomial Formal Verification of Approximate Functions

Polynomial Formal Verification of Approximate Functions Automated polynomial formal verification using generalized binary decision diagram patterns

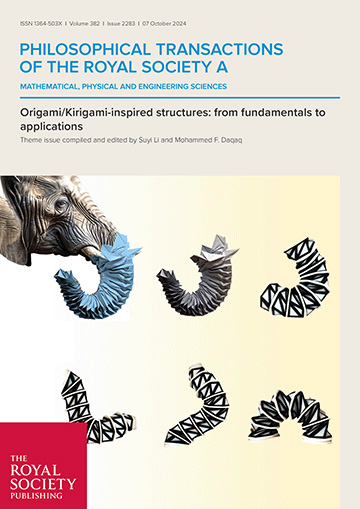

Automated polynomial formal verification using generalized binary decision diagram patterns